集成电路(IC)密度的增大和对市场领导地位的不断角逐要求半导体制造商推出更加复杂的器件。为赢得成功,制造商必须使用由不同专业领域的设计专家组成的多个团队和复杂的项目工作流程,以期最大限度地提高器件的差异化和团队的生产效率。因此,IC项目承担的业务风险不断增大。

达索系统半导体行业解决方案体验( Silicon Thinking Industry Solution Experience )可提供一整套IC设计和工程性能强化组合,有助于降低项目风险,缩短产品上市进程,提升产品质量和良品率。半导体行业解决方案体验通过以下途径实现这些优势:• 高效率知识产权(IP)管理和重复利用

• 可管理设计收敛的图形分析

• 面向所有设计团队提供最新设计数据即时访问

• 从需求到确认和验证,提供端到端可跟踪能力

• 封装可靠性仿真和测试

• 增强型产品种类和缺陷管理

借助该解决方案组合,半导体制造商能更加快速方便地应对更高芯片复杂性、更低功耗、更快量产速度以及更高良品率四大需求同时带来的重重挑战。

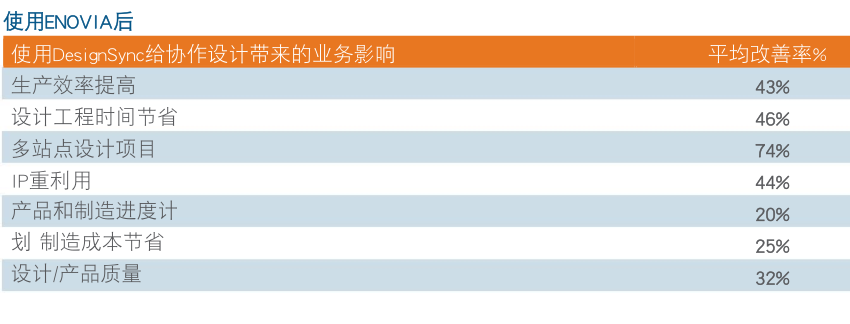

01 实现面向复杂半导体项目的协作设计达索系统半导体协作设计流程结合ENOVIA ® Pinpoint ® 提供的深度设计分析功能和ENOVIA Synchronicity ® DesignSync ® 提供的设计数据管理功能,能提高IC设计的团队工作效率。截止目前,该流程体验已被世界各地超过120家的IC开发机构用于提高设计团队工作效率。

ENOVIA Synchronicity DesignSync

有助于针对大型分布式项目集中化IC设计数据管理。设计数据可直接从电子设计自动化(EDA)工具中捕获并形成层级化数据结构,进而可用于为分布式设计团队提供业经协调的访问权限。该层级化结构直接支持IP模块装配方法,便于快速设计客户专用IC。它还有助于简化和加快将设计子元件集成到总体IC设计中的进程,从而提升设计的重利用率。

ENOVIA Pinpoint

可为管理人员提供仪表板和图形分析功能,用于评估和加快设计收敛。ENOVIA Pinpoint使用历史时限分析多种设计、仿真和测试数据,可帮助用户判断项目可能与规划时间表存在差异的地方。项目经理和设计人员可使用共享视图制定联合项目管理决策。为帮助确保复杂的一体化设计取得成功,针对协作设计和信息系统建立合适的基础至关重要。达索系统半导体协作设计流程提供以下功能:

·跨大型分布式团队的扩展能力;

·支持IP重利用和变型优化;

·与多个应用平台合作,让设计人员专注设计;

·最大化信息访问能力;

·通过自动先进的分析功能和仪表板加快设计决策制定。

每天都有IC设计流片进度计划被打乱。管理人员知道他们需要更快地评估和解决问题,但在对遗留问题了解有限的情况下,设计完成时间总是会超期一定天数。

潜在的这些问题存在多重挑战:

1) 随着IP模块被加入IC布局规划中,设计收敛的复杂程度呈几何级数增长。

2) 设计收敛需要平衡对功能时序、低功耗、最小布局规划、最大可制造性、高性能(速度)和消除热点之间相互冲突的需求。

3) 需使用不同工具保证对不同规格的合规性。每种工具都会生成不同的数据格式,在没有电子表格的情况下,难以使用一个分析图或分析图表开展比较性分析。

4) 由于为不同工程问题提议的解决方案不同,设计收敛往往要求多重设计/测试/评估迭代,这就会给设计完成时间造成不利影响。

导致这些问题和痛点的原因:

1) 导致延迟和低产品质量的主要原因是IC项目复杂性、低效率设计、测试和结果分析工具受限综合作用的结果。

2) 工程人员和团队之间的不良沟通,导致设计不能按时高质量地完成。沟通可能受地理位置、时区、语言、文化、技能集和流程知识的制约。

3) 协作分析所需的设计工具许可证预算有限。

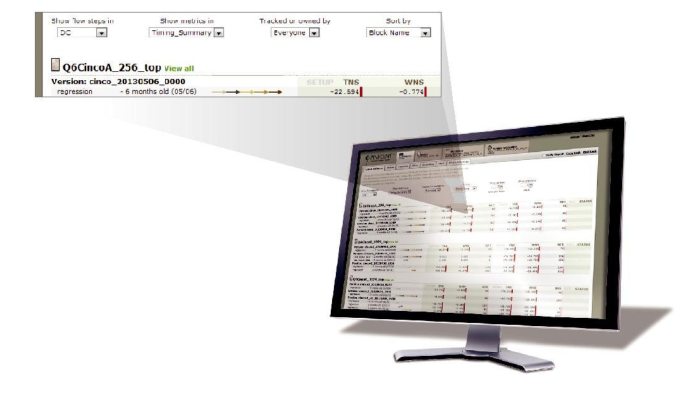

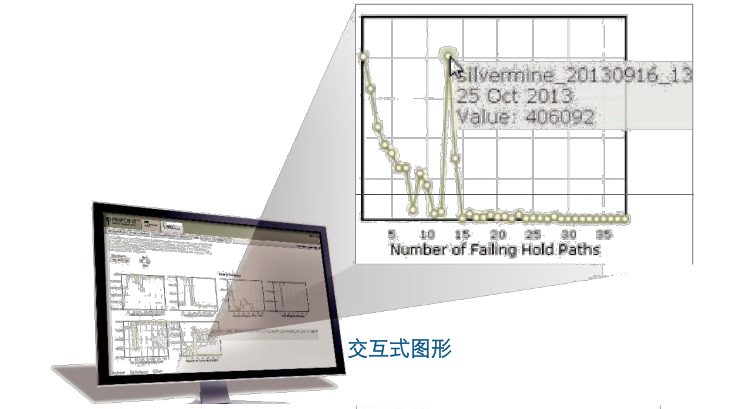

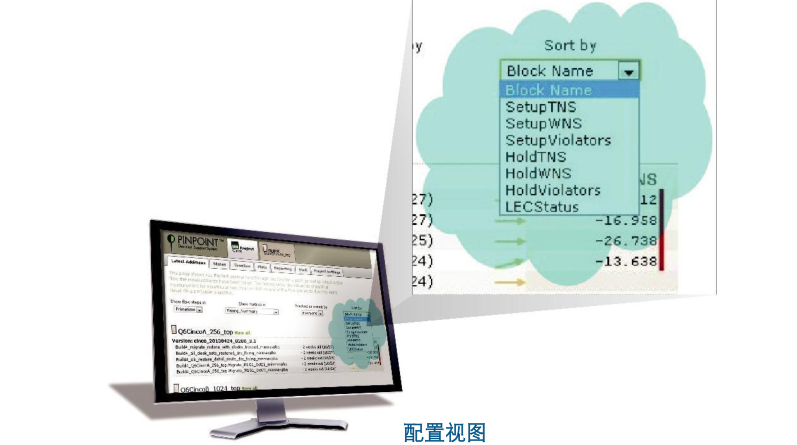

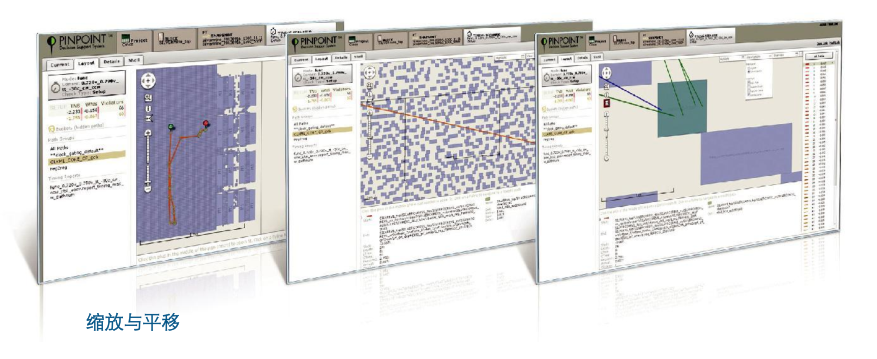

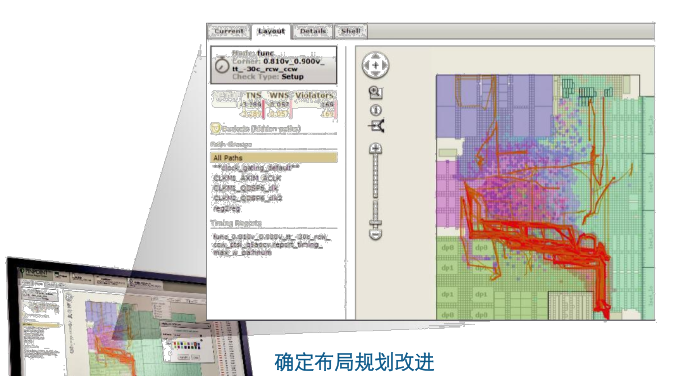

03提炼数据和设计信息分析从物理设计开始,ENOVIA Pinpoint可帮助负责设计收敛的工程人员和管理人员掌握和分析IC设计的整个流程,并针对自身目标确定合适指标。ENOVIA Pinpoint能够搜集大量多维数据,加以分析,并根据历史时限把它们显示在简单的可视化仪表板上,从而帮助用户查看可能偏离正轨的位置。该趋势图有利于营造情景,提升工程人员和管理人员之间的沟通水平。借助 ENOVIA Pinpoint,用户可以获得重要的故障排除信息,从而加快自己的设计进度并进行流片的。数据包括时序、功耗、热量和电阻压降。所有数据都存储在用户通过链接和浏览器可以访问的中央项目数据库中。由于统一的视图可以显示来自不同任务和专业领域的结果,用户设计团队能够更好的沟通和协作,从而跨越设计和确认改进知识共享。

· 交互式图形 – 交互式窗口弹出和向下钻取功能,便于快速找到根源答案

· 可配置视图 – 选择和呈现对用户团队取得成功的最关键数据,迅速发现和调查异常值

· 缩放和平移 – 平移和缩放布局规划图形,以站在较高层次评估问题。然后放大图形,

从事件层面放大到单元层面,进行故障排除

· 总结路径数据 – 发现架构性时序瓶颈

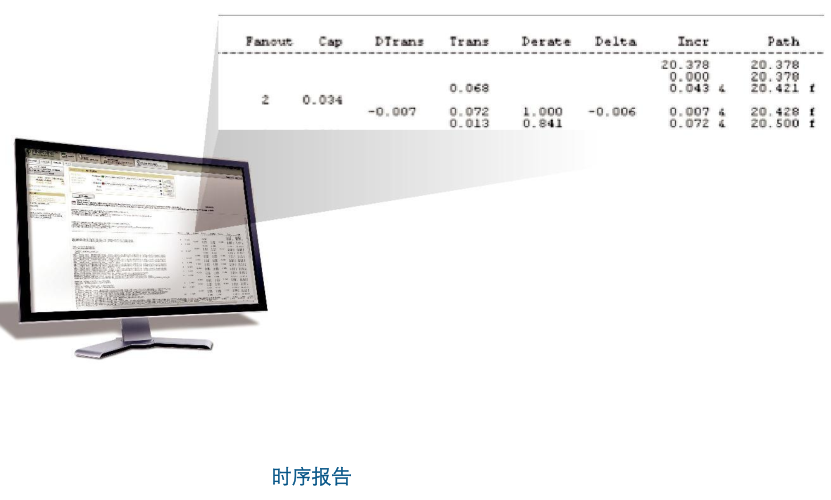

· 时序报告 – 确定具体路径延迟,有针对性地开展重新设计。然后点击通过,查看设计布局规划中被覆盖的时序路径。

06 业经验证的结果

ENOVIA Pinpoint以耗用超过75人年开发的稳定的第五代平台为基础构建,已在IC生产设计领域应用多年。它能够处理和显示半导体物理设计数据,实现半导体项目的快速协作决策。该工具不只是对指标进行跟踪,它能为协作项目管理提供媒介,让处于同一阶段的全体项目成员掌握项目状况。

除了能够改善决策的质量,ENOVIA Pinpoint还有助于聚焦重大决策问题,减少干扰,使用客观数据自动生成状态报告,避免发生主观数据更新。换言之,ENOVIA Pinpoint 有助于提高生产效率,节省用户工程人员在工作上耗用的时间。

如果您对此感兴趣,欢迎问问展商吧!

如果您对此感兴趣,欢迎问问展商吧!

如果您对此感兴趣,欢迎问问展商吧!

如果您对此感兴趣,欢迎问问展商吧!